線上影音

Home > ANSYS Designer 教學 > 傳輸線預模擬

本文最早始於2008以Designer 4.0示範,後於2023更新,以2023R2 Designer circuit示範。截至目前為止,我們都是透過SIwave萃取PCB trace的S-parameter,然後在Designer匯入S參數模型做傳輸線模擬。筆者建議,不要等layout完成再做模擬,最好能先做模擬確認layout的(拓撲)方法,再開始layout,我們稱此手法為"預模擬"(pre-simulation)。

今天要介紹如何在還沒有layout時,引用Designer內現有的傳輸線模型做模擬。以一個特性阻抗50歐姆,總線長1000+1500mils的DDR T型走線為例做說明。

-

初始模擬結果

-

修正後的模擬結果

-

問題與討論

9.1 如何判斷SI pass或fail?

![]()

- 設定傳輸線模型

- 初始模擬結果

-

修正後的模擬結果

- 使用TEE Component

- 問題與討論

9.1 如何判斷SI pass或fail?

Ans:本文所介紹的方法(Pre-simulation),因為沒有使用真正從PCB傳輸線萃取的模型、沒有考慮封裝的影響、沒有同時考慮SI、PI效應、沒有考慮整組bus之間的cross-talk、沒有考慮white noise與jitter budget、沒有考慮內層plane slot所引起的回流路徑不連續性、沒有考慮板上去耦合電容的非理想模型,所以模擬結果只能得到SI相對優劣的趨勢,是用來初估走線的拓撲與終端方式。

若真的需要由模擬來事先判定產品設計的pass or fail,需依該產品的操作頻寬,考慮真實layout的建模與模型萃取(post-simulation),再累積幾次模擬與實做量測結果的比對,才能正確判定。

New a circuit design in AEDT:[Project] \ [Insert Circuit Design]

會跳出一個對話框,可以選擇一些基本的PCB Stack,或是如下所示,直接選None。

在"Components"標籤頁內,選擇Nexxim Circuit Elements展開Distributed\Microstrip\Transmission Lines

介紹兩種較常用的"MS_TRL"、"MS_TRL_Ref",先把"MS_TRL"元件拉進主視窗內。

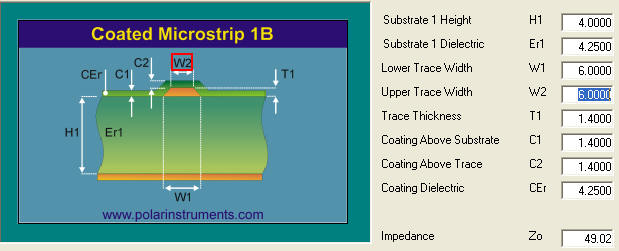

第一次使用此元件時,會先跳出一個疊構設定視窗,如下設定H=4mil、Dk=4.25、Df=0.02、銅厚1.4mil後,按OK。

雙擊"MS_TRL"元件,設定線寬與線長

以Polar驗算目前設計的Microstrip堆疊方式,特性阻抗約為49 Ohm

對於TRL傳輸線模型想進一步學習者,可以參考以下連結

![]() How to Build Transmission Line Model with TRL Tool

How to Build Transmission Line Model with TRL Tool

若想評估放Rs=22 Ohm串聯終端在DDRII T型走線分叉前的效果,又假設分叉前的線長1000mils,分叉後的線長1500mils。使用Micron的DDRII-1066 IBIS作為I/O模型,線路連接如下圖所示

對於以IBIS模型做DDR模擬的細部程序,想進一步學習者,可以參考以下連結

![]() How to Set Up IBIS Model in DDR Simulation

How to Set Up IBIS Model in DDR Simulation

![]() How to Link IBIS Model with Signal Nets Efficiently in DDR Simulation

How to Link IBIS Model with Signal Nets Efficiently in DDR Simulation

5.1 使用DQHALF_1066 ![]()

上圖紅色箭頭所指處,為波形最差發生的時間點,其背後的原因是傳輸線的負載效應(loading effect)。但如果想以ISI (inter-symbol interference) [1]解釋,也是可以。

真的在DDR設計上會需要採用T型走線(一對二)的,並非DQ而是Addr/Cmd/Control,後者也沒有ODT (只有DQ有ODT)。Refer to DDR4

此處取DQ的I/O模型做模擬示範,因為其同時有output/input buffer可以方便使用。所以上圖DDRII-1066雖然是使用DQ的IBIS模型,但UI寬度卻是DDRII-1066 DQ UI的兩倍,也就是所設的UI是符合Addr/Cmd/Control訊號用的。

5.2 使用DQFULL_1066 ![]()

若我們把總線長縮短成2000mils,並且讓Rs盡量往分叉端靠,也就是縮短T型走線的分叉段

6.1 使用DQHALF_1066 ![]()

與5.1的結果相比,明顯變好

6.2 使用DQFULL_1066 ![]()

與5.2的結果相比,也有較好

![]() Layout rule:應該盡量縮短T型走線的分叉段長度。因為線寬不變下走線一分叉,特性阻抗(等效並聯)會剩一半。

Layout rule:應該盡量縮短T型走線的分叉段長度。因為線寬不變下走線一分叉,特性阻抗(等效並聯)會剩一半。

HyperLynx模擬軟體內的line sim. (pre-sim)就是做這檔事[2]。這樣的模擬可以快速抓重點,但無法看出地不連續所造成的效應

從step 5.1複製做修改:如果不想改動Layout而透過使用I/O內部"On-Die_Terminator, ODT"的方法

7.1 ODT_150 (注意ODT要設在Rx端才作用喔)

7.2 ODT_50 (注意ODT要設在Rx端才作用喔)

開ODT即等效於戴維寧終端(並聯Rtt終端上拉至Vtt=VDD/2),雖然可以修飾波形,但會壓縮振幅,所以若能靠縮短走線與正確串接Rs終端值來改善SI,那就別開ODT了。Refer to ODT

只有Addr/Cmd/Ctrl group會需要以T型(一對二)走線,又這些訊號是沒有ODT的,故只能靠加Rs來改善SI

從step 5.1複製做修改

與5.1的結果幾乎相同

[1] 台大吳瑞北老師的講義,說明ISI的worst-case bit pattern for fast-eye analysis

[2] DDRII Design Guide for Consumer by Hynix